Your cart is currently empty!

Singaporese studenten ontwikkelen VHDL in cloud met editor uit Gent

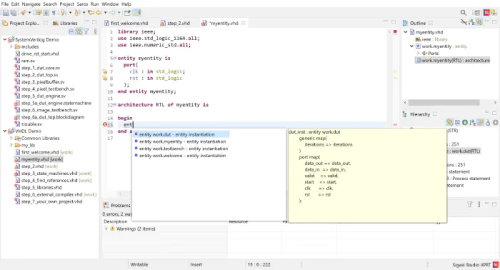

Sigasi uit Gent bouwt samen met het Singaporese Plunify een geïntegreerde IC-ontwerpomgeving voor elektrotechniekstudenten van de National University of Singapore. De partners koppelen de VHDL-editor van de Oost-Vlaamse starter aan het Cloud Compile-platform voor remote simulatie en compilatie van het Aziatische bedrijf. ’De oplossing maakt het VHDL-ontwikkelproces voor onze studenten en onderzoekers een stuk sneller en makkelijker‘, aldus Akash Kumar van de Singaporese universiteit.

Wie op de instelling digitale logica wilde simuleren, was tot voor kort veroordeeld tot een softwarepakket van meerdere gigabytes. Behalve dat het uren kost om te downloaden en te installeren, vereist het veel CPU-kracht, geheugen en schijfruimte op de computer van de gebruiker en is het risico op fouten groot. Bovendien ontbeert de codeontwikkelomgeving features om efficiënt geoptimaliseerde ontwerpen te kunnen implementeren.

De VHDL-editor van Sigasi bevat uitgebreide hulpmiddelen zoals type-time-compilatie, waarmee hardwareontwerpers snel bugs kunnen vinden, functionaliteit kunnen toevoegen aan bestaande projecten en designs kunnen hergebruiken. Door de integratie met Cloud Compile kunnen ze naadloos verdergaan en hun ontwerpen testen in de cloud. Bij een schaarste aan lokale software- en IT-bronnen kunnen ze hun simulatietaken zo uitbesteden aan een dedicated datacentrum, wat resulteert in kortere ontwikkelcycli. 256 bit AES-encryptie met asymmetrische sleutelparen en SSL zorgen hierbij voor de databescherming.