Stacked CMOS marks the end of the roadmap (for now)

Digital circuitry hasn’t always been synonymous with CMOS. Early MOSFET-based logic used either n-type or p-type transistors exclusively to create NMOS and PMOS, respectively. NMOS technology, in particular, proved a popular choice due to its relative simplicity and fast switching. ‘Always-on’ high power consumption weighed it down, however, and it was replaced by CMOS in the 1980s. The latter technology creates complementary pairs of n and p-type transistors, which (ideally) only draw power during a switching operation.

And so, for roughly four decades now, n and p-type switches have been intimately placed together. Mind you, not too closely together, as to prevent capacitance issues from decreasing performance and increasing power consumption. Soon, however, there will be no way around it: in the ever-continuing efforts to increase component density, n en p-type transistors must come closer. Ultimately, they’ll even be stacked on top of each other.

Dielectric wall

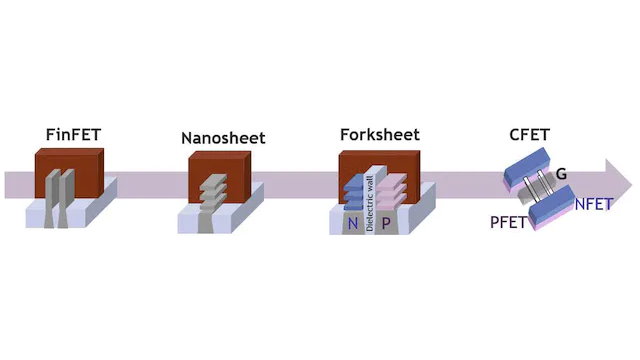

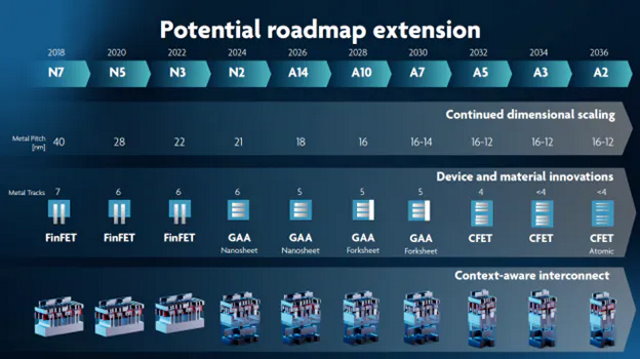

In the late 00s, the trusty ‘flat’ MOSFET steed gave way for the FinFET architecture, in which the channel is raised to a 3D fin structure with the gate draped over it on three sides. This allows for more effective pinching off current. The FinFET’s successor, the gate-all-around (GAA) transistor with gates completely enveloping channels is even more proficient at that. Full-scale GAA adoption in commercial production is expected at upcoming nodes in a year or so.

These new architectures keep the scaling game going but don’t necessarily push n and p-type transistors closer together. Apart from shrinking features, chipmakers have focused on other ways to save on precious wafer area through a broad set of innovations commonly known as design technology co-optimization (DTCO). For example, by optimizing the performance of individual fins in FinFETs, fewer of them are needed, saving on space. Essentially, scaling became no longer ‘merely’ a matter of manufacturing ICs from building blocks that are essentially the same from one generation to the next, just smaller.

As well as helping to keep the shrink going, minimizing the physical separation of n and p-type is a natural extension of DTCO techniques. Imec has already proposed the forksheet FET, which allows for a much tighter spacing of nFET and pFET devices by placing them side-by-side, separated by a thick isolating dielectric ‘wall.’ This architecture also saves on dummy fins that are typically required between n and p-FinFETs.

Appended

Ultimately, chipmakers will be looking to bring the n-to-p horizontal separation to zero by stacking GAA-type nFETs and pFETs on top of each other. At this point, features are so small that two transistors occupying the space of one on the wafer isn’t even the main benefit of this so-called complementary FET (CFET) technology; simplification of transistor terminal access is. At these scales, connecting all components reliably is extremely challenging.

In time, CFETs will incorporate new ultra-thin 2D monolayer materials with an atomic thickness, like tungsten or molybdenum disulfide, Imec says. Such stacked-FET devices incorporating 2D materials currently mark the end of the CMOS roadmap, which isn’t to say new innovations won’t be appended, of course.

The forksheet FET will transition to CFET around the 2032 timeframe. TSMC has revealed that it has working CFETs in the lab, but won’t confirm when or even if they’ll be introduced in mass production. The foundry expects GAA-type devices, like FinFETs, to last at least multiple generations. The CFET also features on Intel’s roadmap, but no details on its adoption have been put forward.